| ■社名 : メンター・グラフィックス・ジャパン株式会社 ■部署 : コーポレート・マーケティング部 ■住所 : 〒140-0001 東京都品川区北品川4-7-35御殿山ヒルズ ■TEL : 03-5488-3035 FAX : 03-5488-3032 ■E-Mail: mktg_mgj@mentor.com ■URL :http://www.mentorg.co.jp/ |

|

|

|

|

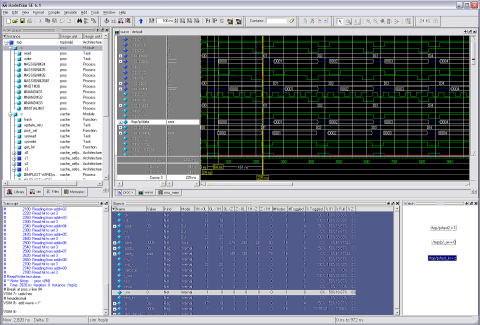

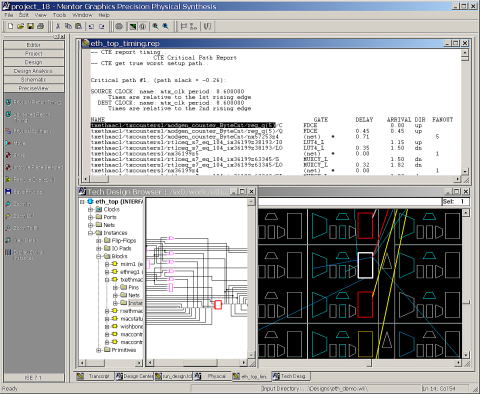

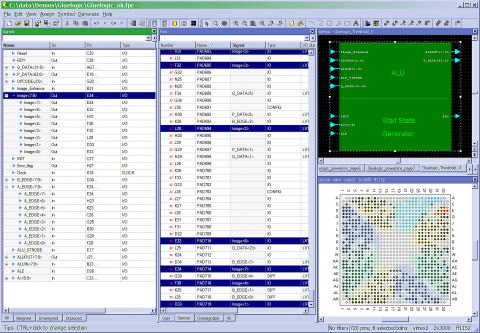

| ■出展概要 | ModelSim: ModelSimはシミュレータに求められる機能やフローを高いレベルで実現しています。ブロックレベルや設計初期におけるバグ改修や解析フローにおいては、Dataflow、Watchウィンドウなどが波形やソースコードと連動することで数十倍もの生産性向上を実現します。チップレベルやリグレッション検証時においては、最新VPOTアルゴリズムによる高速化オプティマイズやシミュレーションファームによる高い生産性向上を実現します。 Precision Synthesis: 配線遅延が全体の70%以上も占める先進のFPGAデバイスにおいて、タイミングが収束しない問題はクリティカルと言えます。配置配線を何度も実行したり前工程へと戻るフローでは、プロジェクトの終了が予測できません。Precision Synthesisは単一のデータモデルに対して、ASEオプティマイズ、Precise Timingによる高度なタイミング解析、PreciseView機能による配置の改善、フィジカルな要素を考慮したリタイミング、レプリケーションなど、多くのテクノロジを集約させたツールです。 I/O Designer: I/O DesignerはFPGA設計とPCB設計との間のブリッジとして機能します。従来それぞれ別々のプロセスで設計していたPCB/FPGAフローはもはや意味を成さないばかりか、設計時間をいたずらに遅延させていました。I/O Designerはデータ管理ツールとしても機能します。FPGAとPCBそれぞれの設計フローを監視し、行われた変更を管理することによって2つのフロー間の一貫性を保ちます。I/O Designerは設計フローに沿って最上流のHDL記述からPCBレベルのシンボルまで、またFPGA配線ツールに必要な物理ピン情報まで、ユニークな管理プロセスを提供します。 |

| ●ModelSim |

|---|

| ●Precision Synthesis |

| ●I/O Designer |

|

|---|

|

|