| ■社名 : メンター・グラフィックス・ジャパン株式会社 ■部署 : コーポレート・マーケティング部 ■住所 : 〒140-0001 東京都品川区北品川4-7-35御殿山ヒルズ ■TEL : 03-5488-3035 FAX : 03-5488-3032 ■E-Mail: mktg_mgj@mentor.com ■URL :http://www.mentorg.co.jp/ |

|

■出展概要 |

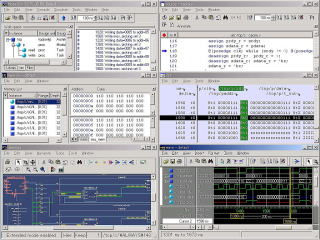

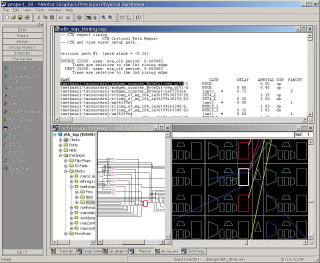

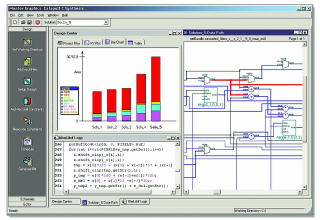

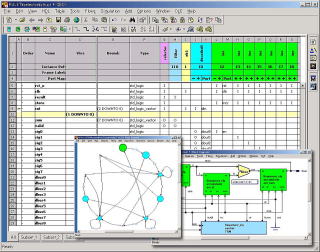

超高速HDLシミュレータModelSim、C/C++アルゴリズムベース合成Catapult C Synthesis、FPGA論理合成Precision、HDLトータル設計/設計マネジメントHDL Designer Seriesによるメンター・グラフィックスのトータルFPGAフローを紹介します。ぜひブースにお立ち寄りください。 ● ModelSim 最新VOPTによる高速化のためのオプティマイズフロー、DataflowやWatchウィンドウを搭載し、波形やソースコードと組み合わせることで数十倍もの生産性を実現するデバッグフロー、バグ発見からその修正を見極めるためのインタラクティブな解析フロー等、シミュレータに求められる機能やフローを高いレベルで実現しています。 ● Catapult C Synthesis 入力言語を完全アンタイムの C/C++ にすることで、通信やネットワーク、画像処理などに用いられるアルゴリズム記述を直接読み込み、論理合成可能な RTL、高速検証が可能な SystemC 検証モデルを出力します。これは単なる高位合成ではなく、アルゴリズム・ドメインから多彩なアーキテクチャ・ドメインへの移行を意味します。 ● Precision Synthesis 単一のデータモデルに対して、ASEオプティマイズ、Precise Timingによる高度なタイミング解析、PreciseView機能による配置の改善、フィジカルな要素を考慮したリタイミング、レプリケーションなど、メンターが持つ様々なテクノロジを集約させた論理合成・物理合成の環境です。 ● HDL Designer Series 設計資産の再利用、設計プロジェクト管理とバージョン管理、設計データのアーカイブ化、ドキュメント化、そしてイントラネット化に対応します。また、設計の仕様書に使われることの多いスプレッドシートと設計データの完全な一貫性を保証するIBD設計手法を提供します。 |

|

|

|---|---|

|

|