| ■社名 : 株式会社ソリトンシステムズ ■部署 : LSIシステムオペレーション ■住所 : 〒160-0022 東京都新宿区新宿2−4−3 ■TEL : 03-5360-3851 FAX : 03-3356-6440 ■E-Mail: information@lsi.soliton.co.jp ■URL : http://soliton.co.jp |

|

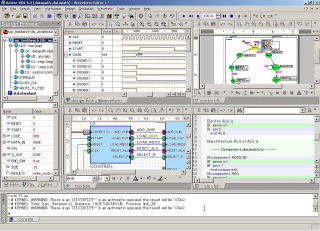

| ■出展概要 | Active-HDLは、1997年にリリースされて以来、世界で10,000人以上のエレクトロニクス設計者によって使用されています。これだけ多くの設計者に広まった理由は、その使い易さとコストパフォーマンスの良さです。 Active-HDLには、グラフィカルデザイン作成機能、波形エディタによるテストパターン生成機能、VHDL/Verilog/EDIF混在対応の高速シミュレーションエンジン、多彩なデバッグ機能が搭載されており、FPGA設計・検証での生産性を向上します。 FPGA設計・検証のデザインフローをサポートする機能として、フローコントロールマネージャを装備しています。フローコントロールマネージャに論理合成ツール・配置配線ツールをプラグインし、Active-HDLからそれらのツールの起動、デザインデータの受け渡し、オプション設定、ツールの実行を行うことができます。また、全てのFPGAベンダ用の最適化されたコンパイル済Verilog及びVHDL ライブラリを提供しています。 MATLAB/Simulink協調検証インターフェースやSWIFTインターフェースといった独自のインターフェースやSystemCとHDLの混在検証、コードカバレッジ機能、HDLコードからブロックダイアグラム・ステートマシンへ変換する機能などによって、設計者が検証に必要とするあらゆるシチュエーションをサポートしています。 次世代設計言語として注目されているSystemVerilogのシミュレーションも可能です。SystemVerilogを試験的に評価される際に他の環境に移行することなActive-HDLで行うことができます。 |